Combining AND logic gates and inverting high-current bipolar outputs, the UDN2540B and A2540SLB quad Darlington power drivers provide interface between low-level signal-processing circuits and power loads totaling 360 W. Each of the four independent outputs can sink up to 1.8 A in the on state with peak inrush currents to 2.5 A. The four power outputs are each comprised of an open-collector Darlington driver and an internal flyback/clamp diode for switching inductive leads. They feature a minimum breakdown and sustaining voltage of 50 V. The logic inputs are compatible with TTL and 5 V CMOS logic systems.

Typical applications include print heads, relays, solenoids, and dc stepping motors. These drivers can also be used to drive high-current incandescent lamps, LEDS, and heaters.

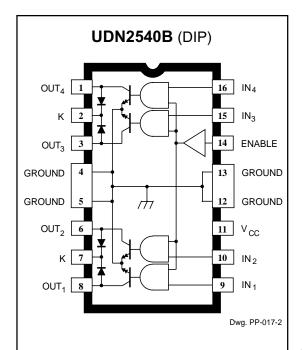

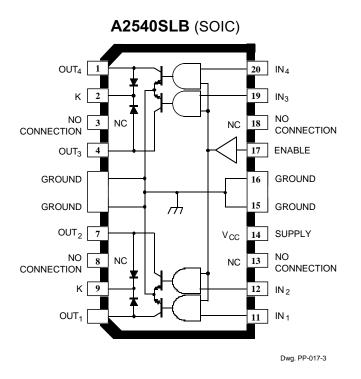

The UDN2540B is supplied in a 16-pin batwing power DIP; the A2540SLB is supplied in a 20-lead batwing power SOIC for surface-mount applications. The batwing construction provides for maximum package power dissipation in a standard construction. At 25°C, and with pcb copper foil heat dissipators at the ground tabs, either package is capable of safely dissipating more than 2 W.

### ABSOLUTE MAXIMUM RATINGS at T<sub>A</sub> = 25°C

| Output Voltage, V <sub>OUT</sub> <b>50 V</b>  |

|-----------------------------------------------|

| Output Current, I <sub>OUT</sub> (peak) 2.5 A |

| (continuous)1.8 A                             |

| Logic Supply Voltage, V <sub>CC</sub>         |

| Input Voltage, V <sub>IN</sub>                |

| Package Power Dissipation,                    |

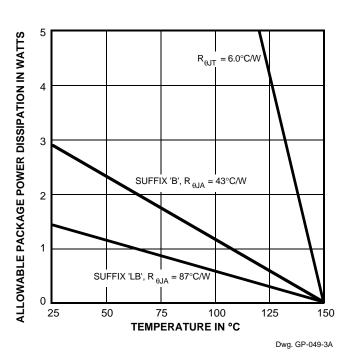

| P <sub>D</sub> See Graph                      |

| Operating Temperature Range,                  |

| T <sub>A</sub> 20°C to +85°C                  |

| Storage Temperature Range,                    |

| T <sub>S</sub> 55°C to +150°C                 |

#### **FEATURES**

- 1.8 A Continuous Output Current

- Output Voltage to 50 V

- TTL and 5 V CMOS Compatible Inputs

- Efficient Input/Output Pinning

- Integral Transient-Suppression Diodes

- Replaces L6221A and L6221CD

Always order by complete part number:

| Part Number | Package              |

|-------------|----------------------|

| UDN2540B    | 16-pin batwing DIP   |

| A2540SLB    | 20-lead batwing SOIC |

$R_{\theta JA}$  is measured on typical two-sided PCB with minimal copper ground area. For the SOIC, adding 3.57 in² copper ground area will reduce the thermal resistance to 52°C/W (2.4 W allowable package power dissipation at 25°C). See Application Note 29501.5, *Improving Batwing Power Dissipation*.

#### **TRUTH TABLE**

| ENABLE | IN <sub>N</sub> | OUT <sub>N</sub> |

|--------|-----------------|------------------|

| Н      | Н               | ON               |

|        | L               | OFF              |

| L      | Х               | OFF              |

X = Don't care.

## ELECTRICAL CHARACTERISTICS at $T_A$ = 25°C, $T_J \leq$ 150°C, $V_{CC}$ = 4.75 V to 5.25 V.

|                             |                      |                                                                           | Limits |      |      |       |

|-----------------------------|----------------------|---------------------------------------------------------------------------|--------|------|------|-------|

| Characteristic              | Symbol               | Test Conditions                                                           | Min.   | Тур. | Max. | Units |

| Output Leakage Current      | I <sub>CEX</sub>     | $V_{OUT} = 50 \text{ V}, V_{IN} = 0.8 \text{ V}, V_{EN} = 2.4 \text{ V}$  | _      | <1.0 | 100  | μΑ    |

|                             |                      | V <sub>OUT</sub> = 50 V, V <sub>IN</sub> = 2.4 V, V <sub>EN</sub> = 0.8 V | _      | <1.0 | 100  | μΑ    |

| Output Sustaining Voltage   | V <sub>CE(sus)</sub> | I <sub>OUT</sub> = 1.8 A, L = 3.0 mH                                      | 50     | _    | _    | V     |

| Output Saturation Voltage   | V <sub>CE(SAT)</sub> | $I_{OUT} = 600 \text{ mA}, V_{IN} = V_{EN} = 2.4 \text{ V}$               | _      | 0.9  | 1.0  | V     |

|                             |                      | I <sub>OUT</sub> = 1.0 A, V <sub>IN</sub> = V <sub>EN</sub> = 2.4 V       | _      | 1.0  | 1.2  | V     |

|                             |                      | I <sub>OUT</sub> = 1.8 A, V <sub>IN</sub> = V <sub>EN</sub> = 2.4 V       | _      | 1.3  | 1.6  | V     |

| Input Voltage               | Logic 1              | $V_{IN(1)}$ or $V_{EN(1)}$                                                | 2.4    | _    | _    | V     |

|                             | Logic 0              | V <sub>IN(0)</sub> or V <sub>EN(0)</sub>                                  | _      | _    | 0.8  | V     |

| Input Current               | Logic 1              | $V_{IN(1)}$ or $V_{EN(1)} = 2.4 \text{ V}$                                | _      | _    | 10   | μΑ    |

|                             | Logic 0              | $V_{IN(0)}$ or $V_{EN(0)} = 0.8 \text{ V}$                                | _      | _    | -100 | μΑ    |

| Total Supply Current        | I <sub>CC</sub>      | $V_{IN}^* = V_{EN} = 2.4 \text{ V}, V_{CC} = 5.0 \text{ V},$              | _      | 14   | 20   | mA    |

|                             |                      | Outputs Open                                                              |        |      |      |       |

|                             |                      | $V_{IN}^* = V_{EN} = 0.8 \text{ V}, V_{CC} = 5.0 \text{ V}$               | _      | 0.4  | 2.0  | mA    |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | I <sub>F</sub> = 1.0 A                                                    | _      | 1.3  | 1.6  | V     |

|                             |                      | I <sub>F</sub> = 1.8 A                                                    | _      | 1.6  | 2.0  | V     |

| Clamp Diode Leakage Current | I <sub>R</sub>       | V <sub>R</sub> = 50 V                                                     | _      | <1.0 | 100  | μΑ    |

Typical Data is for design information only.

Negative current is defined as coming out of (sourcing) the specified terminal.

As used here, -100 is defined as greater than +10 (absolute magnitude convention) and the minimum is implicitly zero.

<sup>\*</sup>All inputs simultaneously, all other tests are performed with each input tested separately.

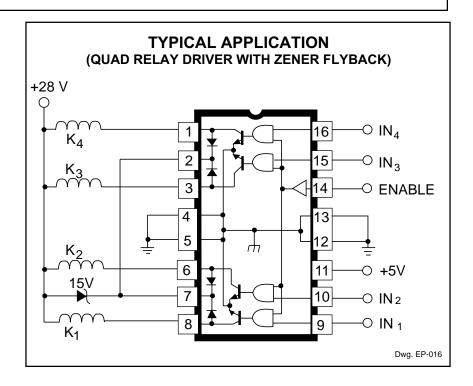

#### **APPLICATIONS INFORMATION**

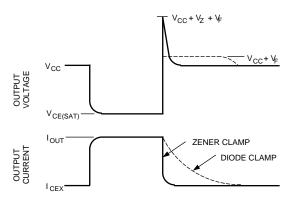

A typical application is shown for driving four high-current relays, solenoids, or print heads. A Zener diode is used to increase the flyback voltage, providing a much faster inductive load turn-off current decay, resulting in faster dropout (reduced relay contact arcing), and improved performance. The maximum Zener voltage, plus the load supply voltage, plus the flyback diode forward voltage must not exceed the device's rated sustaining voltage.

With external control circuitry, the ENABLE input can be used for chopper (PWM) applications. If the ENABLE input is not used, it should be tied high.

All inputs will float high if open circuited.

Dwg. WP-001

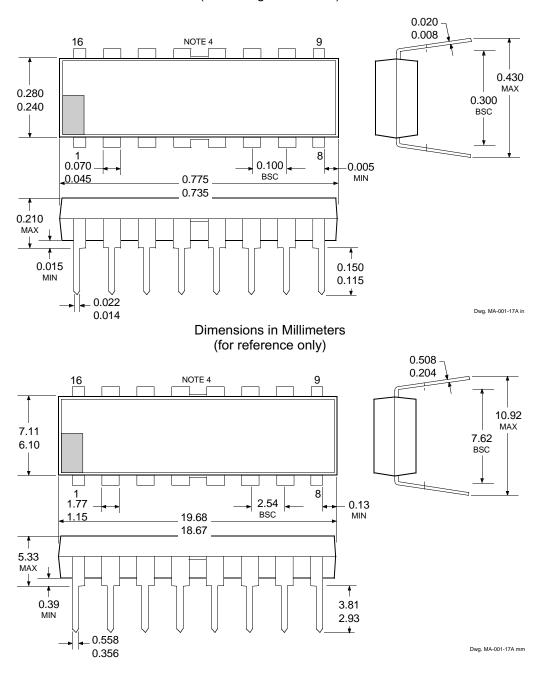

#### **UDN2540B**

Dimensions in Inches (controlling dimensions)

- NOTES: 1. Leads 1, 8, 9, and 16 may be half leads at vendor's option.

- 2. Lead thickness is measured at seating plane or below.

- 3. Lead spacing tolerance is non-cumulative.

- 4. Webbed lead frame. Leads indicated are internally one piece.

- 5. Exact body and lead configuration at vendor's option within limits shown.

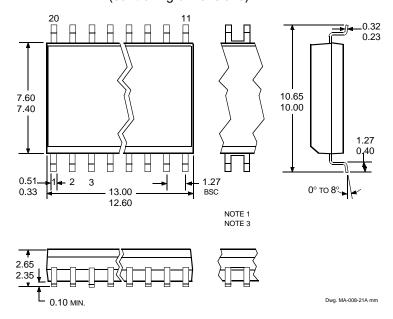

#### **A2540SLB** Dimensions in Inches (for reference only) 0.0125 0.0091 0.419 0.2992 0.2914 0.394 0.050 0.016 Н 0.013 2 3 0.050 0° TO 8° ✓ 0.5118 0.4961 NOTE 1 NOTE 3 0.0926 0.1043 L<sub>0.0040 MIN.</sub>

#### **Dimensions in Millimeters** (controlling dimensions)

Dwg. MA-008-21A in

NOTES: 1. Webbed lead frame. Leads 5, 6, 15, and 16 are internally one piece.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Exact body and lead configuration at vendor's option within limits shown.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.